Góc kỹ thuật

PID là gì

Quá trình PID tấm pin – nỗi lo hiệu suất của hệ thống solar

Nhận dạng ảnh hưởng PID trên tấm pin Thin-Film

PID (Potential Induced Dagradation) của tấm pin có thể xuất hiện và gia tăng rất nhanh chóng trong một khoảng thời gian ngắn làm ảnh hưởng đến hiệu suất toàn hệ thống.

Các yếu tố ảnh hưởng đến tấm pin theo thời gian

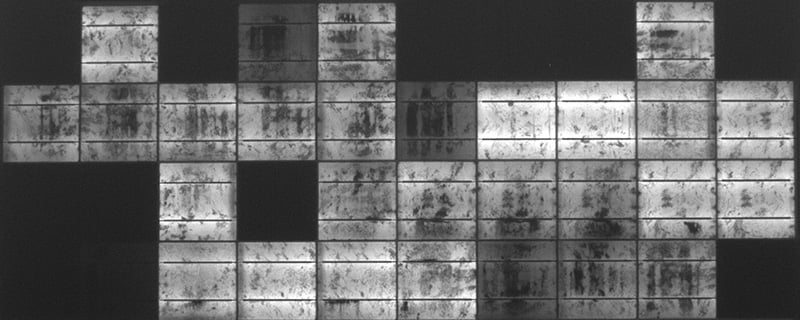

Các tấm cell màu đen đã bị ảnh hưởng của PID

1.Điện áp của giàn pin so với đất

Các tấm pin mặt trời thường có điện áp hoạt động vào khoảng 30V. Khi các tấm pin kết nối thành từng string thì con số này sẽ tăng lên từ 300-500V và có thể cao hơn với các hệ thống lớn. Chúng ta cùng xem xét các loại inverter và ảnh hưởng của chúng đến điện áp của hai cực của giàn pin so với đất. Giả sử với hệ thống 400V:

- Inverter không nối đất và có biến áp cách ly: Điện áp chia đối xứng với +200 ở cực dương và -200 ở cực âm.

- Inverter với biến áp cách ly và cực âm nối đất: Cực âm điện áp bằng 0, điện áp ở cực dương là +400V.

- Inverter với biến áp cách ly và cực dương nối đất: Cực dương điện áp bằng 0, điện áp ở cực âm là -400V.

- Inverter không sử dụng biến áp cách ly ( transfomerless): tùy theo thiết kế nhưng thông thường điện áp sẽ được offset về phía âm nhiều hơn. VD: -350V.

2. PID của tấm pin là gì ?

PID xuất hiện chủ yếu ở các tấm pin gần cực âm của string. Điện áp cực âm ( VD -200V) so với khung tấm pin ( được nối đất ) tạo ra lực điện trường làm cho các ion dương từ tấm kín cường lực ( Na+ ) di chuyển vào cell. Các ion Na+ gây ra quá trình ăn mòn điện hoá trên cell dẫn đến suy giảm công suất tấm pin. Đây được gọi là quá trình PID-s.

Điện áp cao còn là nguyên nhân dẫn đến các electron di chuyển ra bên ngoài khung tấm pin và đi xuống đất. Đây được gọi là quá trình PID-p. Cả PID-s và PID-p có thể hoặc không thể hồi phục.

3. Các yếu tố ảnh hưởng đến PID

a. Chủng loại Inverter ảnh hưởng đến PID của tấm pin

Trên thị trường hiện nay phổ biến hai loại inverter là có biến áp ( transfomer ) và không có biến áp ( transfomerless) . Inverter transformer sử dụng biến áp với chức năng nâng điện áp AC lên bằng với điện áp của lưới. Sử dụng biến áp đồng nghĩa với việc inverter đã được cách ly DC và AC, do đó chúng ta có thể nối cực âm của giàn pin xuống đất. Điều này giúp cực âm của giàn pin có điện áp so với đất bằng 0 và loại bỏ hoàn toàn PID.

Tuy nhiên do vấn đề giá thành, các inverter trên thị trường đa số là loại transfomerless dẫn đến cực âm của giàn pin không được phép nối đất.

Phân bố điện áp cực của string so với đất ( Inverter có biến áp )

Phân bố điện áp cực của string so với đất ( Inverter không có biến áp )

b. Các thông số của cell và tấm pin

Kính cường lực, lớp EVA, lớp chống phản xạ (ARC) là những yếu tố ảnh hưởng đến PID.

Bản thân kính cường lực với tỉ lệ Natri Cacbonat càng cao sẽ làm tăng PID trong hệ thống.

Lớp EVA (Ethyl Vinyl Acetate) có chứa các loại Axit acetic khi kết hợp với nhiệt độ và độ ẩm cao sẽ làm cho các ion từ tấm kính bám nhiều hơn trên bề mặt cell. Nogài ra, lớp chống phản xạ ARC sử dụng vật liệu chính là Silic nitrua. Tỉ lệ Silic và Nitơ cùng với độ dày của ARC sẽ ảnh hưởng đến PID.

Lớp ARC càng dày sẽ làm cho PID càng phát triển mạnh

c. Các thông số môi trường

Độ ẩm và nhiệt độ là hai yếu tố ảnh hưởng đến PID của tấm pin nhiều nhất chúng làm gia tăng dòng rò PID-p.

4. PID ảnh hưởng thế nào đến hệ thống

PID là một quá trình phức tạp và có nhiều yếu tố ảnh hưởng. Nhìn chung PID sẽ làm giảm công suất phát và tuổi thọ của tấm pin. PID của tấm pin tăng dần theo thời gian, ảnh hưởng đến Voc và hệ số FF ( Fill Factor ) của tấm pin. Sự suy giàm ảnh hưởng đến tấm pin bị PID và cả string chứa tấm pin. Công suất phát của hệ thống có thể suy giảm lên đến 90% theo thời gian.

5. Các phương pháp làm giảm PID

a. Sử dụng các thiết bị hỗ trợ

Sử dụng inverter trasformer có thể giúp loại bỏ PID của tấm pin khỏi hệ thống. Còn đối với các inverter tansformer less, chúng ta có các thiết bị như PV Off Set box của SMA…

Vào buổi tôi, khi điện áp của giàn pin nhỏ hơn giá trị ngưỡng, Offset Box sẽ nâng điện áp của toàn bộ giàn pin lên mức điện áp cao (từ +400V cho đến +1000V so với đất ). Quá trình này giúp đảo ngược sự phân cực xảy ra trên tấm pin vào ban ngày. Đối với hệ thống đã bị PID trong thời gian dài, việc tái tạo lại các tấm pin sẽ mất khoảng 1/2 khoảng thời gian tính từ khi PID xuất hiện. Công suất AC cấp cho bộ Offset Box là rất nhỏ chỉ khoảng 3W.

b. Tấm pin và cell

Chất liệu kính có ít tỉ lệ Natri giúp giảm PID, lớp EVA chúng ta có thể chuyển sang loại vật liệu POE (Poly Olefin Elastomer) giúp giảm PID. tỉ lệ Si:N , độ dày và độ đồng nhất của ARC có thể giúp tấm pin giảm ảnh hưởng của PID

c. Thông số môi trường

Điều tốt nhất là chúng ta nên sử dụng các tấm pin đã đạt tiêu chuẩn IEC để giảm rủi ro do PID gây ra khi hệ thống hoạt động

Các tấm pin đang được test theo tiêu chuẩn IEC TS 62804-1. Quá trình test tấm pin được đặt trong nhiệt độ 80 độ C và độ ẩm trên 85% trong vòng 96 tiếng. Giúp đánh giá ảnh hưởng của các ứng suất lên tấm pin năng lượng mặt trời.